# 2x30W I<sup>2</sup>S Input, Inductor Free, Stereo Class D Amplifier

## ■ FEATURE

- Power supply:

- PVDD: 4.5V – 22V; -DVDD: 3.3V

- Audio Performance

- BTL, 2x33W (PVDD=22V,  $R_L=8\Omega$ , THD+N=10%)

- PBTL, 50W (PVDD=22V,  $R_L=4\Omega$ , THD+N=1%)

- THD+N=0.05% (PVDD=12V,  $R_L=4\Omega$ , Po=1W)

- Noise: 100uV (Gain = 19dBV, A weighted)

- Low Quiescent Current

- 12mA at PVDD = 12V, no filter

- High efficiency in 1SPW mode (>90%)

- Inductor-free Operation (Ferrite Bead) and EMC compliant for most cases

- Flexible Audio I/O

- I<sup>2</sup>S, LJ, RJ, TDM input

- 8, 16, 32, 44.1, 48, 88.2, 96, 192kHz Sample Rates

- General Operational Features

- Hardware or Software Control mode

- 4 Programmable I<sup>2</sup>C Addresses

- Spread Switching Frequency for Class D

- Robustness Features

- Clock Error, DC, Over Current, Overvoltage, Undervoltage, and Overtemperature Protection

- Packages: Pb-free Packages, QFN6x6-36L

## ■ GENERAL DESCRIPTION

The HT760 is a stereo Class D audio amplifier with multiple audio format port (I<sup>2</sup>S, LJ, RJ, TDM). It supports a variety of audio clock configurations.

The outputs of the HT760 can be configured to drive two speakers in stereo BTL mode or mono PBTL mode.

The HT760 also includes hardware and software control modes, integrated digital clipper, and a wide power supply operating range to enable use in a multitude of applications.

Advanced EMI Suppression with Spread Spectrum Control enables the use of inexpensive ferrite bead filters while meeting EMC requirements for system cost reduction.

An optimal mix of thermal performance and device cost is provided in the 150-mΩ  $R_{DS(ON)}$  of the output MOSFETs. Additionally, a thermally enhanced 36-Pin QFN provides excellent operation in the elevated ambient temperatures found in modern consumer electronic devices.

## ■ APPLICATIONS

- Bluetooth/Wi-Fi Speakers

- Portable Speakers

- Smart speakers

- LCD TV/Monitor

- Sound Bars, Docking stations, PC Audio

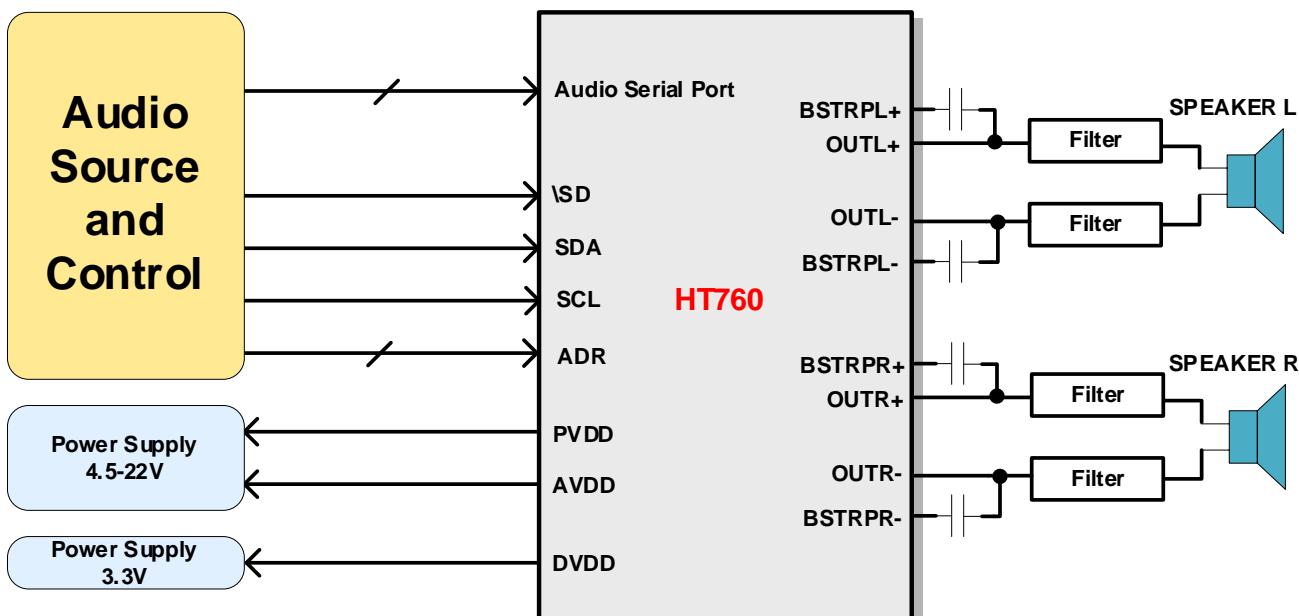

## ■ TYPICAL APPLICATION

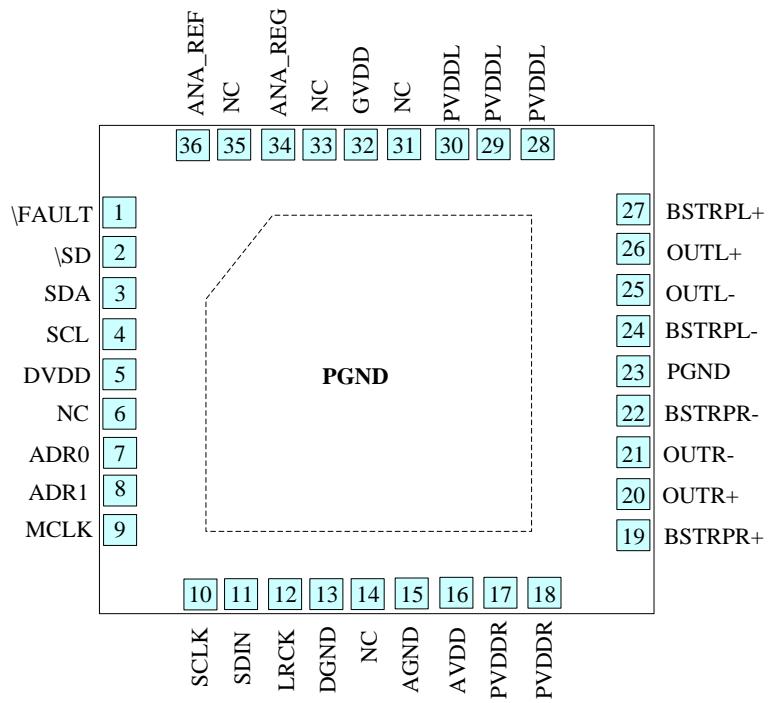

## ■ TERMINAL CONFIGURATION

Top View

## ■ TERMINAL FUNCTION

| Terminal No.      | Name   | I/O <sup>1</sup> | Description                                                                                                                                              |

|-------------------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | \FAULT | OD               | Speaker amplifier fault terminal, which is pulled LOW when an internal fault occurs, open-drain output.                                                  |

| 2                 | \SD    | I                | Places the speaker amplifier in shutdown mode while pulled low level.                                                                                    |

| 3                 | SDA    | I                | I <sup>2</sup> C data input pin.                                                                                                                         |

| 4                 | SCL    | I                | I <sup>2</sup> C clock input terminal.                                                                                                                   |

| 5                 | DVDD   | P                | Power supply for the internal digital circuitry                                                                                                          |

| 6, 14, 31, 33, 35 | NC     | -                | Not connected inside the device (they be connected to ground for better thermal performance; however, they can be used as routing channels if required.) |

| 7                 | ADR0   | I                | Determine the I <sup>2</sup> C Address of the device                                                                                                     |

| 8                 | ADR1   | I                | Determine the I <sup>2</sup> C Address of the device                                                                                                     |

| 9                 | MCLK   | I                | Master Clock used for internal clock tree, sub-circuit/state machine, and Serial Audio Port clocking                                                     |

| 10                | SCLK   | I                | Bit clock for the digital signal that is active on the serial data port's input data line                                                                |

| 11                | SDIN   | I                | Data line to the serial data port                                                                                                                        |

| 12                | LRCK   | I                | Word select clock for the digital signal that is active on the serial port's input data line                                                             |

| 13                | DGND   | G                | Ground for digital circuitry (NOTE: This pin should be connected to the system ground)                                                                   |

| 15                | AGND   | G                | Ground for analog circuitry (NOTE: This pin should be connected to the system ground)                                                                    |

<sup>1</sup>: I: Input; O: Output; G: Ground; P: Power; BST: BOOT Strap; OD: Open drain

|    |         |     |                                                                                                                                                                                                                                                                                   |

|----|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 | AVDD    | P   | Power supply for internal analog circuitry                                                                                                                                                                                                                                        |

| 17 | PVDDR   | P   |                                                                                                                                                                                                                                                                                   |

| 18 | PVDDR   | P   | Power Supply for internal power circuitry of Channel R                                                                                                                                                                                                                            |

| 19 | BSBRPR+ | BST | Connection point for the OUTR+ bootstrap capacitor, which is used to create a power supply for the high-side gate drive for OUTR+                                                                                                                                                 |

| 20 | OUTR+   | O   | Positive pin for differential speaker amplifier output R                                                                                                                                                                                                                          |

| 21 | OUTR-   | O   | Negative pin for differential speaker amplifier output R                                                                                                                                                                                                                          |

| 22 | BSBRPR- | BST | Connection point for the OUTR- bootstrap capacitor, which is used to create a power supply for the high-side gate drive for OUTR-                                                                                                                                                 |

| 23 | PGND    | G   | Ground for power device circuitry (NOTE: This terminal should be connected to the system ground)                                                                                                                                                                                  |

| 24 | BSTRPL- | BST | Connection point for the OUTL- bootstrap capacitor, which is used to create a power supply for the high-side gate drive for OUTL-                                                                                                                                                 |

| 25 | OUTL-   | O   | Negative pin for differential speaker amplifier output L                                                                                                                                                                                                                          |

| 26 | OUTL+   | O   | Positive pin for differential speaker amplifier output L                                                                                                                                                                                                                          |

| 27 | BSBRPL+ | BST | Connection point for the OUTL+ bootstrap capacitor, which is used to create a power supply for the high-side gate drive for OUTL                                                                                                                                                  |

| 28 | PVDDL   | P   |                                                                                                                                                                                                                                                                                   |

| 29 | PVDDL   | P   |                                                                                                                                                                                                                                                                                   |

| 30 | PVDDL   | P   |                                                                                                                                                                                                                                                                                   |

| 32 | GVDD    | O   | Voltage regulator derived from PVDD supply (NOTE: This pin is provided as a connection point for filtering capacitors for this supply and must not be used to power any external circuitry)                                                                                       |

| 34 | ANA_REG | P   | Voltage regulator derived from AVDD supply (NOTE: This terminal is provided as a connection point for filtering capacitors for this supply and must not be used to power any external circuitry)                                                                                  |

| 36 | ANA_REF | P   | Connection point for internal reference used by ANA_REG filter capacitors. <b>And connect to system GND.</b>                                                                                                                                                                      |

| EP | PGND    | G   | Provides both <b>electrical and thermal connection</b> from the device to the board. <b>A matching ground pad must be provided on the PCB and the device connected to it via solder.</b> For proper electrical operation, this ground pad must be connected to the system ground. |

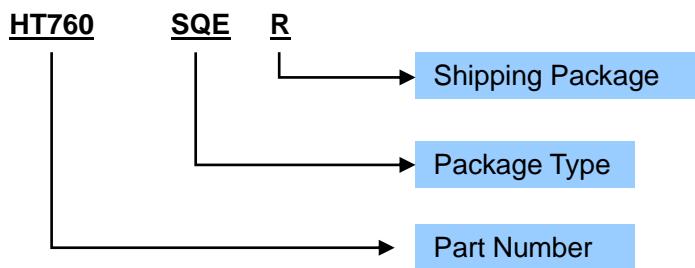

## ■ ORDERING INFORMATION

| Ordering Number | Package Type | Marking                         | Operating Temperature Range | MOQ/Shipping Package    |

|-----------------|--------------|---------------------------------|-----------------------------|-------------------------|

| HT760SQER       | QFN6x6-36L   | HT760SQ<br>YYYMAAB <sup>1</sup> | -25°C~85°C                  | Tape and Reel / 2500pcs |

### Ordering Number

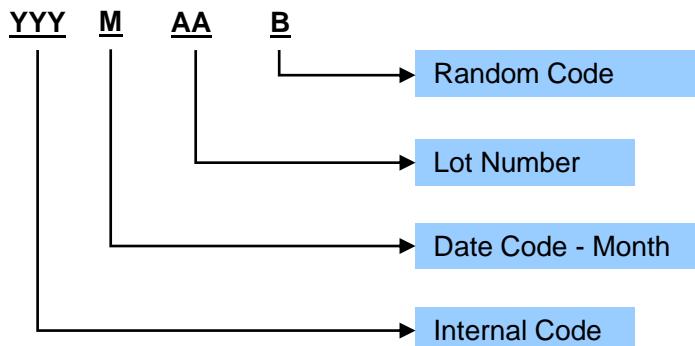

### Production Tracking Code

<sup>1</sup> YYYMAAB is production tracking code

**IMPORTANT NOTICE****注意**

Heroic Electronic Technology (Jiaxing) Co., Ltd (HT) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any products or services. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

禾润电子科技（嘉兴）有限公司（以下简称HT）保留对产品、服务、文档的任何修改、更正、提高、改善和其他改变，或停止提供任何产品和服务的权利。客户在下单和生产前应确保所得到的信息是最新、最完整的。

HT assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using HT components.

HT对相关应用的说明和协助以及客户产品的板级设计不承担任何责任。

HT products are not authorized for use in safety-critical applications (such as life support devices or systems) where a failure of the HT product would reasonably be expected to affect the safety or effectiveness of that devices or systems.

HT的产品并未授权用于诸如生命维持设备等安全性极高的应用中。

The information included herein is believed to be accurate and reliable. However, HT assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

本文中的相关信息是精确和可靠的，但HT并不对其负责，也不对任何可能的专利和第三方权利的侵害负责。

Following are URLs and contacts where you can obtain information or supports on any HT products and application solutions:

下面是可以联系到我公司的相关链接和联系方式：

**禾润电子科技（嘉兴）股份有限公司**

**Heroic Electronic Technology (Jiaxing) Co., Ltd.**

地址：浙江省嘉兴市凌公塘路3339号JRC大厦A座三层

Add: A 3rd floor, JRC Building, No. 3339, LingGongTang Road, Jiaxing, Zhejiang Province

Sales: 0573-82585539, sales@heroic.com.cn

Support: 0573-82586151, support@heroic.com.cn

Fax: 0573-82585078

Website: [www.heroic.com.cn](http://www.heroic.com.cn); [wap.heroic.com.cn](http://wap.heroic.com.cn)

Wechat MP: HEROIC\_JX

请及时关注禾润官方微信公众号，随时获取最新产品信息和技术资料！